How it came to be Back in October 2022, we initiated a component bank under the SLRC branch of the Electronic Club. Our goal was…

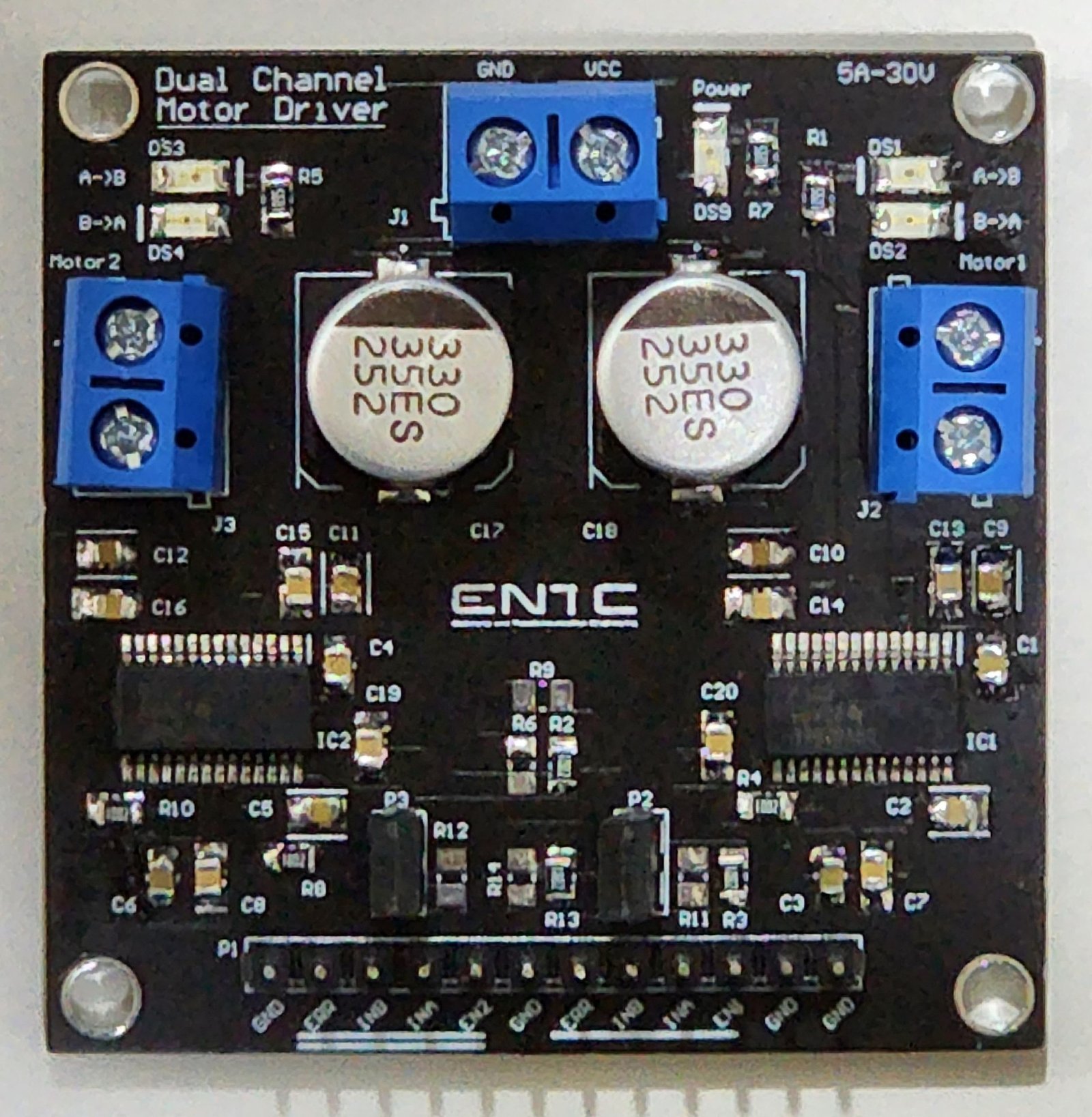

View More The Story of the ENTC Motor DriverOur Experience at the IEEE International Future Energy Challenge 2022

This blog post is dedicated to demonstrate the project of University of Moratuwa for the IEEE International Future Energy Challenge 2022, which is a prestigious…

View More Our Experience at the IEEE International Future Energy Challenge 2022Our Journey to Win the Silver Award in the InnovateFPGA Design Contest

We, Pahan, Chathuni and Pamuditha, are three undergraduate students from Sri Lanka, a small island in the Indian Ocean. But we were never ones to…

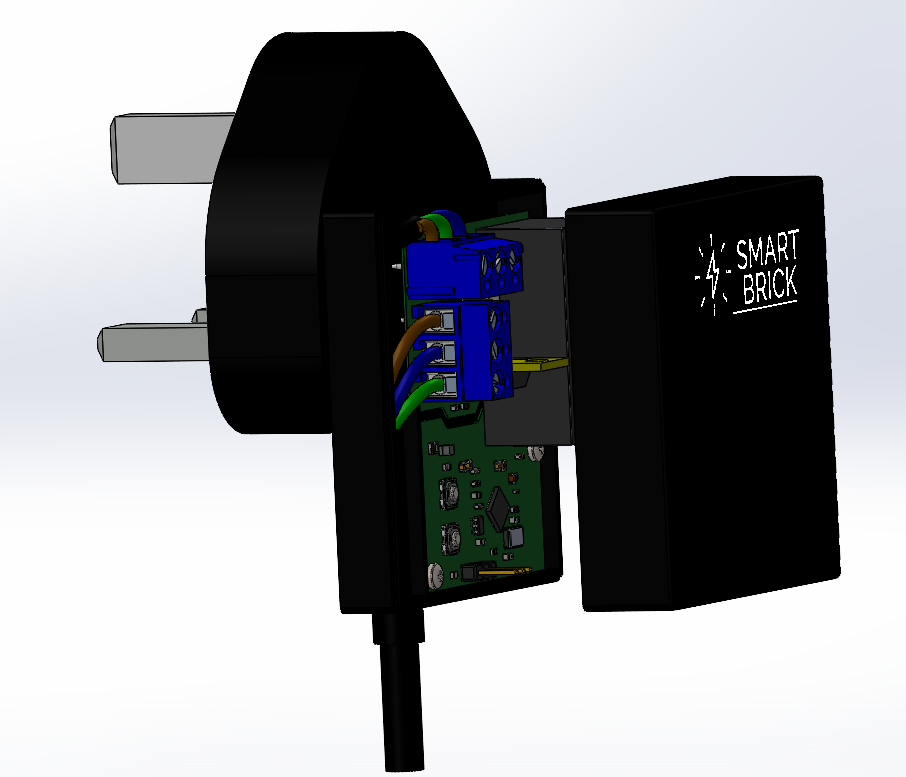

View More Our Journey to Win the Silver Award in the InnovateFPGA Design ContestThe Smart Brick – The Design of a Wi-Fi Controlled Switch

We designed an automatic switch that can be controlled via Wi-Fi to connect electrical appliances to power. Our design is similar to a plug top…

View More The Smart Brick – The Design of a Wi-Fi Controlled SwitchTask Specific Robot using Cypress PSoC

This project was done with the collaboration between Minoo Gunawardena from Monash University, Malaysia and Chathuni Wijegunawardana. A mobile robot was created and controlled using…

View More Task Specific Robot using Cypress PSoCDesigning an Alarm Clock

We designed a fully functional alarm clock for our 2nd semester lab project at the Department of of Electronics and Telecommunication Engineering at University of…

View More Designing an Alarm ClockDesign of an Alarm Clock – Microproduct Alarm Timing

This blog is about my 2nd semester lab project at Department of Electronic and Telecommunication Engineering at University of Moratuwa. The task was to design…

View More Design of an Alarm Clock – Microproduct Alarm TimingImplementation of a BCD to 7 Segment Display on FPGA

What is a BCD to 7 Segment Display? A BCD to 7 segment combinational logic circuit gets a decimal digit as its input and converts…

View More Implementation of a BCD to 7 Segment Display on FPGADesign of Displaying 0-15 on 7-segment Display using Logic Gates

In another blog, I explained how to develop the digital design for a BCD to 7-segment decoder on FPGA. But in that case, we only…

View More Design of Displaying 0-15 on 7-segment Display using Logic GatesDesign of BCD to 7 Segment Display Decoder using Logic Gates

A BCD to 7 segment combinational logic circuit gets a decimal digit as its input and converts the signal to suite a 7 segment display.…

View More Design of BCD to 7 Segment Display Decoder using Logic Gates